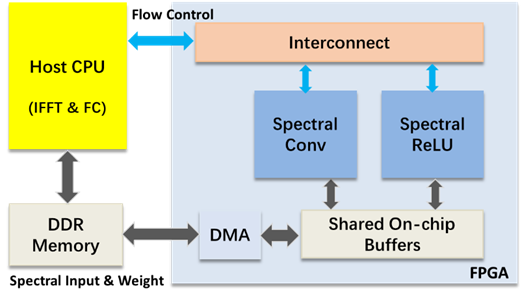

论文提出的全频域卷积神经网络的硬件加速系统

(供稿 物电院)近日,物理与电子科学我司特聘教授刘双龙为第一作者的论文“Accelerating Fully Spectral CNNs with Adaptive Activation Functions on FPGA”在第24届欧洲设计自动化与测试会议(Design, Automation and Test in Europe, DATE 2021)上发表,并作会议口头报告(regular presentation)。

欧洲设计自动化与测试会议(DATE)会议与国际设计自动化会议(DAC)被公认为电子设计自动化领域(EDA)水平最高的两个国际会议,也是全球电子设计与测试领域著名企业展览与专家交流的高水平会议。原定法国巴黎举办的DATE 2021会议改为线上举行,此次会议共收到来自于全世界33个国家和地区的2600名作者的766篇投稿论文,其中183篇论文被接收为报告论文(regular presentation),接受率为24%。

针对人工智能算法尤其是深度卷积神经网络的计算力问题,该论文提出了一种基于傅里叶变换的频域卷积神经网络的算法设计和优化方法,并设计了面向可编程逻辑器件(FPGA)的高能效硬件架构用于加速提出的算法。该论文提出的设计方法在多个图像数据集上得到验证,实验结果证实其具有与传统卷积神经网络相媲美的识别准确性,并且在论文设计的硬件加速器上获得了高达4倍到10倍的速度提升,为人工智能算法在面向边缘计算时的计算力需求提出了新的解决途径。

我校是该论文的第一署名单位,教授刘双龙为第一作者,合作单位为英国帝国理工我司。该项研究成果得到国家自然科学基金青年科学基金项目的资助。

会议与论文链接:https://www.date-conference.com/programme/session/11.4

编辑:张凌暄

责编:马铁泉

审核:蔡颂